# AN32257A

# INTEGRATED WIRELESS POWER SUPPLY RECEIVER, Qi (WIRELESS POWER CONSORTIUM) COMPLIANAT

#### FEATURES

- Integrated Wireless Power Receiver Solution

- Synchronous Full Bridge Rectifier control

- Input Voltage Range : VCC: 5 V ~ 19 V

- Over Temperature, Voltage, Current protection

- Under voltage lockout function

- Thermal Shut Down

- LED Indicator

- I<sup>2</sup>C Interface

- Package WLCSP

#### DESCRIPTION

AN32257A is a Wireless Power System Controller IC which is designed for Qi compliance defined by Version 1.1 of the System Description Wireless Power Transfer, Volume 1 for Low Power from Wireless Power Consortium. AN32257A is a controller IC to be used as the power receiver on a wireless power mobile device.

A Qi compliance wireless power mobile device with AN32257A built-in could work with any wireless power base station which is Qi compliance.

#### APPLICATIONS

- WPC Compliant Receivers

- · Cell Phones, Smart Phones

- · Headsets

- · Digital Cameras

- Tablets

- · Portable Media Players etc.

The product specifications described in this book are subject to change without notice for the product which is currently under development. At the final stage of your design, purchasing, or use of the product, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                 | Rating        | Unit | Notes |

|--------------------------------|------------------------|---------------|------|-------|

|                                | V <sub>RECT</sub>      | 20            | V    | *1    |

| Supply voltage                 | V <sub>EXT</sub>       | 6.9           | V    | *1    |

|                                | V <sub>VIO</sub>       | 6             | V    | *1    |

| Output Current                 | I <sub>RECT</sub>      | —             | А    | *1    |

| Operating free-air temperature | T <sub>opr</sub>       | – 30 to + 85  | °C   | *2    |

| Storage temperature            | T <sub>stg</sub>       | – 50 to + 125 | °C   | *2    |

| ESD                            | HBM (Human Body Model) | TBD           | kV   | _     |

Notes) This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guarantee able as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

\*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2:Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25 °C.

#### POWER DISSIPATION RATING

| PACKAGE   | $\theta_{JA}$ | PD ( Ta = 25 °C) | PD ( Ta = 85 °C ) | Notes |

|-----------|---------------|------------------|-------------------|-------|

| WLCSP Typ | TBD °C / W    | TBD W            | TBD W             | *1    |

Note). For the actual usage, please refer to the PD-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

#### CAUTION

Although this has limited built-in ESD protection circuit, but permanent damage may occur on it. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Pin Name          | Min.     | Тур. | Max. | Unit | Notes |

|----------------------|-------------------|----------|------|------|------|-------|

|                      | V <sub>RECT</sub> | 4.4      | 8    | 19   |      |       |

| Supply voltage range | V <sub>EXT</sub>  | 4.4      | 5    | 6    | V    | *1    |

|                      | V <sub>VIO</sub>  | 3.2(TBD) | 3.3  | 5.5  |      |       |

Note) Do not apply external currents and voltages to any pin not specifically mentioned.

Voltage values, unless otherwise specified, are with respect to GND.

\*1 : The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

#### **ELECRTRICAL CHARACTERISTICS**

Cout = 4.7  $\mu F,\,V_{RECT}$  =  $\,8$  V,  $T_a$  = 25  $^{\circ}C$   $\pm$  2  $^{\circ}C$  unless otherwise noted.

|                 | Devenester                          | Cumhal               | Condition                                                                                                         |      | Limits |      | Unit | Note |

|-----------------|-------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|------|--------|------|------|------|

| Parameter       |                                     | Symbol               | Symbol Condition                                                                                                  |      | Тур    | Max  | Unit | Note |

| Cu              | rrent Consumption                   |                      |                                                                                                                   |      |        |      |      |      |

|                 | Quiescent current                   | I <sub>STBY</sub>    |                                                                                                                   |      | TBD    |      | mA   | -    |

| UV              | LO                                  |                      |                                                                                                                   |      |        |      |      |      |

|                 | Undervoltage lock-out               | V <sub>UVLO</sub>    | V <sub>RECT</sub> : 0V -> 5V                                                                                      | 3.99 | 4.2    | 4.41 | V    |      |

|                 | Hysteresis on UVLO                  | V <sub>UVLOHY</sub>  | V <sub>RECT</sub> : 5V -> 3V                                                                                      | _    | 0.4    | _    | V    |      |

| ٥v              | P                                   |                      |                                                                                                                   |      |        |      |      |      |

|                 | Input overvoltage threshold         | V <sub>OVP</sub>     | V <sub>RECT</sub> : 5V -> 19V                                                                                     | 17   | 18     | 19   | V    |      |

|                 | Hysteresis on OVP                   | V <sub>OVPOHY</sub>  | V <sub>RECT</sub> : 19V -> 5V                                                                                     | _    | 3      | _    | V    |      |

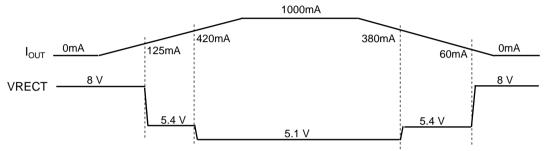

| V <sub>RE</sub> | ECT (5W, LDO 5V mode )              |                      |                                                                                                                   |      |        |      |      |      |

|                 | V <sub>RECT</sub> Threshold1        | V <sub>RECTTH1</sub> | I <sub>LOAD</sub> <125mA(TBD)                                                                                     |      | 8      |      | V    |      |

|                 | V <sub>RECT</sub> Threshold2        | V <sub>RECTTH2</sub> | 125mA <i<sub>LOAD&lt;420mA<br/>(TBD)</i<sub>                                                                      |      | 5.4    |      | V    |      |

|                 | V <sub>RECT</sub> Threshold3        | V <sub>RECTTH3</sub> | 420mA <i<sub>LOAD (TBD)</i<sub>                                                                                   |      | 5.1    |      | V    |      |

| V <sub>RE</sub> | CT (5W, LDO 7V mode )               |                      |                                                                                                                   |      |        |      |      |      |

|                 | V <sub>RECT</sub> Threshold4        | V <sub>RECTTH4</sub> |                                                                                                                   |      | TBD    |      | V    |      |

|                 | V <sub>RECT</sub> Threshold5        | V <sub>RECTTH5</sub> |                                                                                                                   |      | TBD    |      | V    |      |

|                 | V <sub>RECT</sub> Threshold6        | V <sub>RECTTH6</sub> |                                                                                                                   |      | TBD    |      | V    |      |

| ου              | TPUT                                |                      |                                                                                                                   |      |        |      |      |      |

|                 |                                     | V <sub>OUT1</sub>    | VRECT=8V ,<br>I <sub>LOAD</sub> =10mA                                                                             | 4.85 | 5      | 5.15 | V    |      |

|                 | V <sub>OUT</sub> (5W, LDO 5V mode ) | V <sub>OUT2</sub>    | VRECT=5.1V ,<br>I <sub>LOAD</sub> =1000mA                                                                         | 4.76 | _      | _    | V    |      |

|                 | V <sub>OUT</sub> (5W, LDO 6V mode ) | V <sub>OUT3</sub>    | $\label{eq:VRECT=9V} \begin{array}{l} VRECT=9V \ , \\ I_{LOAD} = 10 mA \\ \mathbf{C}_{OUT} = 10 \muF \end{array}$ |      | 6      |      | V    |      |

|                 | V <sub>OUT</sub> (5W, LDO 7V mode ) | V <sub>OUT4</sub>    | $\label{eq:VRECT=10V} \begin{array}{l} VRECT=10V \ , \\ I_{LOAD}=10mA \\ C_{OUT}=10\muF \end{array}$              |      | 7      |      | V    |      |

### ELECRTRICAL CHARACTERISTICS (Continue)

Cout = 4.7  $\mu F,\,V_{RECT}$  =  $\,8$  V,  $T_a$  = 25  $^{\circ}C$   $\pm$  2  $^{\circ}C$  unless otherwise noted.

| <b>_</b>                                  |                    | 0                                                 |      | Limits |      |      | Nata |

|-------------------------------------------|--------------------|---------------------------------------------------|------|--------|------|------|------|

| Parameter                                 | Symbol             | Condition                                         | Min  | Тур    | Max  | Unit | Note |

| Temperature Detector [Thermistor : Ef     | RTJ0EV104          | F]                                                |      |        |      |      |      |

| Over-temperature Detection Voltage        | V <sub>TH</sub>    | 60 °C detection<br>VTHR : TBD kohm (±1%)          |      | TBD    |      | V    | _    |

| Over-current protection                   |                    |                                                   |      |        |      |      |      |

| Over-current threshold voltage            | V <sub>OCP</sub>   | Difference Voltage<br>between VRECT and<br>ISENSE |      | TBD    |      | V    |      |

| Thermal protection                        |                    |                                                   |      |        |      |      | •    |

| Thermal shutdown temperature              | Tj                 | _                                                 |      | TBD    |      |      | _    |

| Thermal shutdown hysteresis               | T <sub>jhys</sub>  | _                                                 |      | TBD    | _    |      | _    |

| Ext detector                              |                    |                                                   |      |        |      |      |      |

| V <sub>EXT</sub> Rising threshold voltage | V <sub>EXTTH</sub> | _                                                 | 3.99 | 4.2    | 4.41 |      | _    |

| V <sub>EXT</sub> hysteresis               | V <sub>EXTHY</sub> | _                                                 |      | 0.4    |      |      | _    |

| Termination (FULLCH)                      |                    |                                                   |      | •      |      |      | •    |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.0  | _      | _    | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | _                                                 | -0.2 | _      | 0.2  | V    | _    |

| Termination (SELVER)                      |                    |                                                   |      |        |      |      |      |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.0  | _      |      | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | _                                                 | -0.2 | _      | 0.2  | V    | _    |

| Termination (SELHP)                       |                    |                                                   |      |        |      |      |      |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.0  | _      |      | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | _                                                 | -0.2 | _      | 0.2  | V    | _    |

| Termination (SELOSR)                      |                    |                                                   |      |        |      |      |      |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.0  | _      |      | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | _                                                 | -0.2 | _      | 0.2  | V    | _    |

| Termination (NFC)                         |                    |                                                   |      |        |      |      |      |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.0  | _      |      | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | —                                                 | -0.2 | _      | 0.2  | V    | _    |

| Termination (SELHV)                       |                    |                                                   |      |        |      |      |      |

| High input threshold (Termination)        | V <sub>IH1</sub>   | _                                                 | 2.9  | _      |      | V    | _    |

| Low input threshold                       | V <sub>IL1</sub>   | _                                                 | -0.2 | _      | 0.5  | V    | _    |

### ELECRTRICAL CHARACTERISTICS (Continue)

Cout = 4.7  $\mu F,\,V_{RECT}$  =  $\,8$  V,  $T_a$  = 25  $^{\circ}C$   $\pm$  2  $^{\circ}C$  unless otherwise noted.

|           | Parameter                          | Symbol             | Condition                                           |                          | Limits |                          | Unit | Note |

|-----------|------------------------------------|--------------------|-----------------------------------------------------|--------------------------|--------|--------------------------|------|------|

| Farameter |                                    | Symbol Condition   |                                                     | Min                      | Тур    | Max                      | Unit | Note |

| Те        | mination (EXTCLK)                  |                    |                                                     |                          |        |                          |      |      |

|           | High input threshold (Termination) | V <sub>IH1</sub>   | V <sub>IO</sub> = 3.3V                              | V <sub>IO</sub><br>× 0.7 | _      | _                        | V    | _    |

|           | Low input threshold                | V <sub>IL1</sub>   | V <sub>IO</sub> = 3.3V                              | -0.2                     |        | V <sub>IO</sub><br>× 0.3 | V    | _    |

| Те        | rmination (OUTHP)                  |                    |                                                     |                          |        |                          |      | •    |

|           | Output High level                  | V <sub>OH</sub>    | V <sub>IO</sub> = 3.3V<br>I <sub>OUTHP</sub> = -2mA | V <sub>IO</sub><br>× 0.8 |        | _                        | V    |      |

|           | Output Low level                   | V <sub>OL</sub>    | V <sub>IO</sub> = 3.3V<br>I <sub>OUTHP</sub> = +2mA | -0.2                     |        | V <sub>IO</sub><br>× 0.2 | V    |      |

| Те        | rmination (ENI2C)                  |                    |                                                     |                          |        |                          |      |      |

|           | Output High level                  | V <sub>OH</sub>    | V <sub>IO</sub> = 3.3V<br>I <sub>ENI2C</sub> = -2mA | V <sub>IO</sub><br>× 0.8 |        | _                        | V    |      |

|           | Output Low level                   | V <sub>OL</sub>    | V <sub>IO</sub> = 3.3V<br>I <sub>ENI2C</sub> = +2mA | -0.2                     |        | V <sub>IO</sub><br>× 0.2 | V    |      |

| LE        | DCNT                               |                    |                                                     |                          |        |                          |      |      |

|           | LET Sat                            | LED <sub>SAT</sub> | I <sub>LED</sub> = 20mA                             |                          | _      | 0.5                      | V    | —    |

|           | LED Leak                           | LED                | LED = 7.5V                                          |                          |        | 10                       | uA   | —    |

### ELECRTRICAL CHARACTERISTICS (Continue)

Cout = 4.7  $\mu F,\,V_{RECT}$  =  $\,8$  V,  $T_a$  = 25  $^{\circ}C$   $\pm$  2  $^{\circ}C$  unless otherwise noted.

|     | Parameter                            | Symbol | Condition                                                    |                     | Limits |                             | Unit | Note |

|-----|--------------------------------------|--------|--------------------------------------------------------------|---------------------|--------|-----------------------------|------|------|

|     | Farameter                            | Symbol | Condition                                                    | Min                 | Тур    | Max                         | Unit | Note |

| 120 | bus (Internal I/O stage characterist | ics)   |                                                              |                     |        |                             |      |      |

|     | Low-level input voltage              | VIL1   | Voltage which is<br>recognized as SDA and<br>SCL Low Level   | -0.5                |        | $0.3 \times V_{IO}$         | V    | *1   |

|     | High-level input voltage             | VIH1   | Voltage which is<br>recognized as SDA and<br>SCL High Level  | $0.7 \times V_{IO}$ |        | V <sub>IOmax</sub><br>+ 0.5 | V    | *1   |

|     | SDA<br>Low-level output voltage 1    | VOL1   | V <sub>IO</sub> > 3 V<br>SDA(sink current) = 3 mA            | 0                   |        | 0.4                         | V    | _    |

|     | SDA<br>Low-level output voltage 2    | VOL2   | V <sub>IO</sub> < 3 V<br>SDA(sink current) = 3 mA            | 0                   |        | $0.2 \times V_{IO}$         | V    | _    |

|     | Input current each I/O pin           | IL     | SCL, SDA =<br>0.1 × V <sub>IO</sub> to 0.9 × V <sub>IO</sub> | -10                 |        | 10                          | mA   |      |

|     | SCL clock frequency                  | FOSC   |                                                              | 0                   |        | 400                         | kHz  | _    |

Note) \*1 : The input threshold voltage of I<sup>2</sup>C bus (Vth) is linked to  $V_{IO}$  (I<sup>2</sup>C bus I/O stage supply voltage).

In case the pull-up voltage is not V<sub>IO</sub>, the threshold voltage (Vth) is fixed to ((V<sub>IO</sub> / 2)  $\pm$  (Schmitt width) / 2) and High-level, Low-level of input voltage are not specified.

In this case, pay attention to Low-level (max.) value (V\_{\text{ILmax}}).

It is recommended that the pull-up voltage of  $I^2C$  bus is set to the  $I^2C$  bus I/O stage supply voltage (V<sub>IO</sub>).

Slave address

| A7 | A6 | A5 | A4 | A3 | A2 | A1 |

|----|----|----|----|----|----|----|

| 0  | 0  | 1  | 0  | 0  | 1  | 0  |

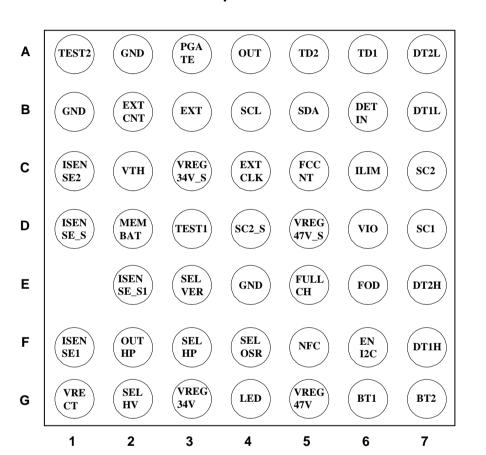

#### Pin Layout

**Top View**

**Product Standards**

# AN32257A

Note). Refer to a "Detail Description" and the "Application Information" for detailed information.

#### **Pin Function**

| Pin No.      | Pin name      | Туре            | Description                                                  |

|--------------|---------------|-----------------|--------------------------------------------------------------|

| A1           | TEST2         | Ι               | TEST Pin                                                     |

| A2,B1,<br>E4 | GND           | GND             | GND Pin                                                      |

| A3           | PGATE         | 0               | LDO Control Switch Pin                                       |

| A4           | OUT           | Ι               | LDO Feed back Pin                                            |

| A5           | TD2           | 0               | Driving Load Capacity for Transmit Pin                       |

| A6           | TD1           | 0               | Driving Load Capacity for Transmit Pin                       |

| A7           | DT2L          | 0               | Rectification Low side Switch Gate Control Pin               |

| B2           | EXTCNT        | 0               | External Switch control Pin                                  |

| В3           | EXT           | Power<br>Supply | External Input Pin for Detection                             |

| B4           | SCL           | Ι               | I2C clock input Pin                                          |

| B5           | SDA           | I/O             | I2C data input/output Pin                                    |

| B6           | DETIN         | Ι               | Wave shaping Pin                                             |

| B7           | DT1L          | 0               | Rectification Low side Switch Gate Control Pin               |

| C1           | ISENSE2       | Ι               | Current Sense Pin2                                           |

| C2           | VTH           | Ι               | Thermistor Connection Pin for abnormal temperature detection |

| C3           | VREG34V<br>_S | 0               | Internal Regulator Output Pin                                |

| C4           | EXTCLK        | Ι               | External CLK Input Pin                                       |

| C5           | FCCNT         | Ι               | Full-Charge Control Pin                                      |

| C6           | ILIM          | Ι               | Programming Pin for the over current limit.                  |

| C7           | SC2           | Ι               | Rectification Detection Pin                                  |

| D1           | ISENSE1_S     | Ι               | Current Sense Pin1                                           |

| D2           | MEMBAT        | 0               | Random Number Memory Time Adjustment Pin                     |

| D3           | TEST1         | 0               | TEST Pin                                                     |

| D4           | SC2_S         | Ι               | Rectification Detection Pin                                  |

| D5           | VREG47V<br>_S | 0               | Internal Regulator Output Pin                                |

| D6           | VIO           | Power<br>Supply | I2C Interface Power Supply Pin                               |

| D7           | SC1           | Ι               | Rectification Detection Pin                                  |

Note). Refer to a "Detail Description" and the "Application Information" for detailed information.

# Product Standards

# AN32257A

#### **Pin Function**

| Pin No. | Pin name   | Туре         | Description                                     |

|---------|------------|--------------|-------------------------------------------------|

| E2      | ISENSE1_S1 | Ι            | Current Sense Pin                               |

| E3      | SELVER     | Ι            | Select WPC Version                              |

| E5      | FULLCH     | Ι            | Full-Charge Signal Pin                          |

| E6      | FOD        | 0            | FOD Correction Pin                              |

| E7      | DT2H       | 0            | Rectification High side Switch Gate Control Pin |

| F1      | ISENSE1    | Ι            | Current Sense Pin                               |

| F2      | OUTHP      | 0            | Output Enable 10W mode Pin                      |

| F3      | SELHP      | Ι            | Select Power 5W or 10W mode Pin                 |

| F4      | SELOSR     | Ι            | Select Outside Sense Resistor                   |

| F5      | NFC        | Ι            | NFC Pin                                         |

| F6      | ENI2C      | 0            | Enable to read or write I2C Pin                 |

| F7      | DT1H       | 0            | Rectification High side Switch Gate Control Pin |

| G1      | VRECT      | Power Supply | Supply Voltage Pin (from Rectifier Circuit)     |

| G2      | SELHV      | Ι            | Select Output Voltage(5V,6V or 7V) Pin          |

| G3      | VREG34V    | 0            | Internal Regulator Output Pin                   |

| G4      | LED        | 0            | LED Driver Pin                                  |

| G5      | VREG47V    | 0            | Internal Regulator Output Pin                   |

| G6      | BT1        | 0            | Boot Strap Pin                                  |

| G7      | BT2        | 0            | Boot Strap Pin                                  |

Note). Refer to a "Detail Description" and the "Application Information" for detailed information.

**Product Standards**

## AN32257A

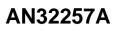

### FUNCTIONAL BLOCK DIAGRAM : Composition corresponding to 5W

**Product Standards**

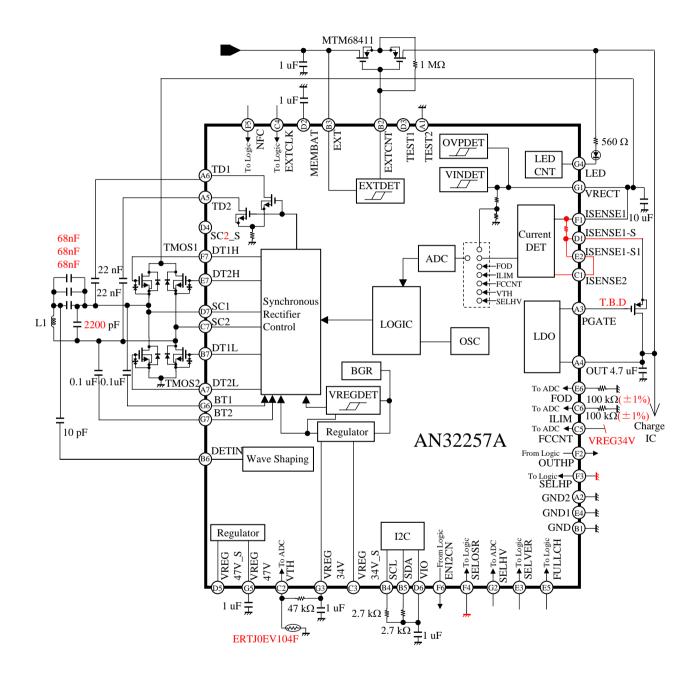

## AN32257A

### FUNCTIONAL BLOCK DIAGRAM : Composition corresponding to 10W

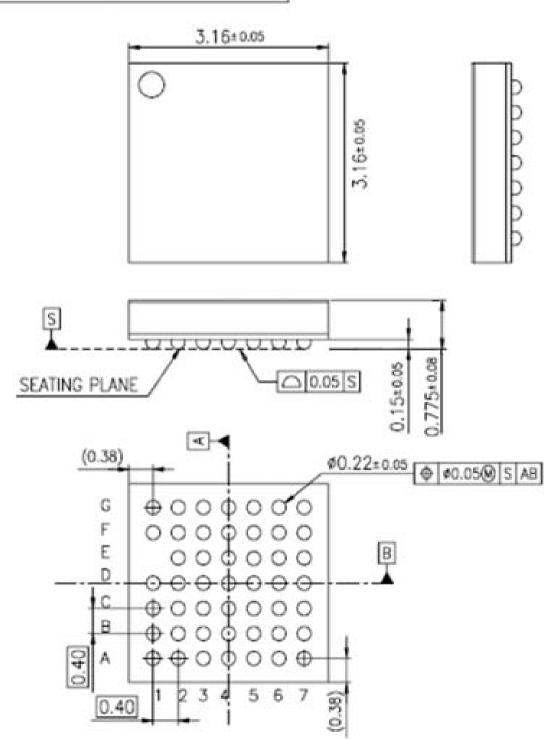

### **PACKAGE INFORMATION (Reference Data)**

Unit : mm

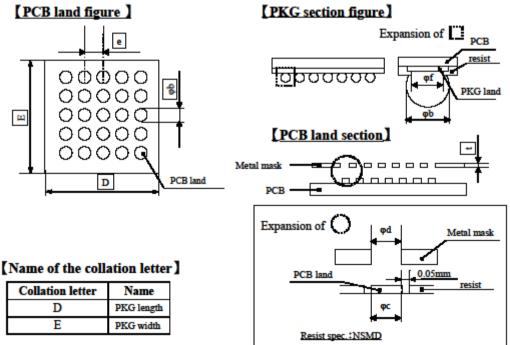

#### The reference spec. of PCB & Mask for WLCSP ver.1.0

Semiconductor Business Group Industrial Devices Company Panasonic Co.,Ltd.

(PCB land +0.10mm (one side +0.05mm))

unit:mm

#### [ Reference spec.]

| Name                 | Symbol | Reference spec. |           |           |           |  |  |

|----------------------|--------|-----------------|-----------|-----------|-----------|--|--|

| Terminal pitch       | е      | 0.50            | 0.50      | 0.40      | 0.30      |  |  |

| PKG land             | φf     | 0.23            | 0.25      | 0.20      | 0.15      |  |  |

| Terminal diameter    | φb     | 0.23            | 0.25/0.31 | 0.20/0.22 | 0.15      |  |  |

| PCB land diameter    | φc     | 0.27            | 0.30      | 0.23      | 0.15~0.18 |  |  |

| Metal mask openning  | φd     | 0.27            | 0.30      | 0.23      | 0.20~0.23 |  |  |

| Metal mask thickness | t      | 0.08~0.11       | 0.08~0.11 | 0.08~0.11 | 0.08~0.11 |  |  |

\*The above size is calculated based on the experiment results by Panasonic Corporation, and is not intended as a guarantee of mounting reliability. Mounting reliability can vary depending on factors such as the equipment specifications and conditions, material specifications and properties, and environmental conditions. To ensure satisfactory results, your company should evaluate and confirm actual mounting performance.

# AN32257A

### **Functional explanation**

1. All the functions

- Programmable Full Charge control setting

- Programmable Over Current Limit

- Selectable WPC Version

- Selectable Full Charge control through External Pin

- Adjustable Foreign Object Detection Threshold

- Selectable Power Range 5W or 10W mode

- Selectable between Internal/External Sense Resistor

- Option to send NFC request

- Selectable Output Voltage

- Report the frequency of the primary side

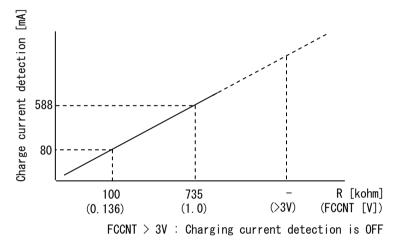

#### Programmable Full Charge Control Setting When the charging current is less than the value set at FCCNT Pin (Pin No. C5). Full Charge will be asserted and the output will be shut-off.

Example: By connecting 100k ohms between FCCNT pin and GND, An End Power Transfer Packet indicating Full Charge will be transmitted to the primary side when the charging current is less than or equal to 80mA (approximately) 5secs after charging begin.

Note: If this function is not required, it can be disable by connecting FCCNT pin to VREG34V.

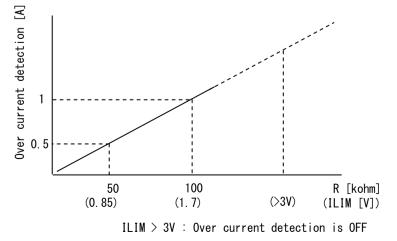

3. Programmable Over Current Limit

If the output current goes beyond the value set at ILIM pin (Pin No. C6), output will be turned off due to Over-current.

Example: By connecting 100k ohms between ILIM pin and GND, End Power Transfer Packet indicating Over Current will be transmitted to the primary side when the output current is more than or equal to 1000mA.

Note: If this function is not required, it can be disable by connecting ILIM pin to VREG34V. Under this condition, the default setting, 1500mA and 2500mA for 5W mode and 10W mode respectively for over-current will be set. 4. Selectable WPC Version

The WPC version can be selected between version 1.1 to 1.0 by connecting SELVER (Pin No. E3) to GND (Default) or VREG34V respectively.

5. Selectable Full Charge control through External Pin

If the FULLCH Pin (No. E5) is supplied an external voltage of level VREG34V, End Power Transfer Packet indication Full Charge will be transmitted to the primary side. Note that this external pin takes priority over the setting at FCCNT Pin.

6. Adjustable Foreign Object Detection Threshold The Received Power value that will be sent to the primary side for Foreign Object Detection can be adjusted through the FOD Pin (Pin No. E6). Example: By connecting 100k ohms between FOD pin and GND, the Received Power that will be transmitted to the primary side will be offset by +0W.

Note: If this function is not required, it can be disable by connecting FOD pin to VREG34V.

Selectable Power Range 5W or 10W mode The Desired Power can be selected through SELHP (Pin No. F3). By connecting SELHP pin to GND, 5W (Default) will be selected. When SELHP pin is connected to VREG34V, 10W mode will be selected.

Note: 10W mode will only operate will the primary side is NN32251A. If the primary side is not NN32251A, it will operate in 5W mode even though SELHP may be set for 10W mode.

#### **Functional explanation (Continue)**

8. Selectable between Internal/External Sense Resistor

The current sensing resistors can be selected through SELOSR (Pin No. F4). When SELOSR is tied to GND, Internal sensing resistors (Default) will be used, otherwise, if SELOSR is tied to VREG34V, the sensing resistors shall be external discrete resistor.

Note: When set to 10W mode, please tied SELOSR pin to VREG34V so that external sensing resistors can be used.

This is reduce the heat generated when using 10W mode.

9. Option to send NFC request

User has the option to send NFC to the primary side by setting NFC pin (Pin No. F5) to VREG34V level. NFC request will be indicated to the primary side only when the primary side is NN32251A. And, in the event that the primary side support NFC transfer, power will be cut-off to faciliate NFC transfer.

10. Selectable Output Voltage

Output Voltage can be selected through SELHV (Pin No. G2). The setting is as follows: OPEN:5V GND:7V VREG34V:6V

11. Report the frequency of the primary side When an external clock of frequency 4MHz to 19MHz is input through EXTCLK (Pin No. C4), the transmit frequency during charging will be computed and recorded in the internal registers. User can check this value through Serial Bus (I2C).

#### **Application information**

1. Full charge detection : FCCNT (Pin No. C5)

The threshold for full charge current can be preset through FCCNT pin. When the charging current falls below this threshold, full charge will be indicated to the primary side through End Power Transfer Packet. At the same time, the output will be turned off. Note that this happens only 5 seconds after charging begins.

This setting for the full charge current can be done through connecting resistor between FCCNT terminal and GND.

As an example, when 100kohm is connected between FCCNT terminal and GND, the threshold current is 80mA (Refer to the graph below).

When this function is not required, please connect FCCNT terminal directly to VREG34V.

2. Over current detection : ILIM (Pin No. C6)

The threshold for Over Current Detection can be set through ILIM terminal.

As an example, when 100kohm is connected between ILIM terminal and GND, the threshold current will be about 1A. If the current goes beyond 1A under this setting, End Power Transfer Packet will be transmitted to a primary side indicating Over Current. At the same time, the output will be turned off. When this function is not required, please connect ILIM terminal directly to VREG34V.

In this case, Over Current threshold will be 1.5A and 2.5A for 5W and 10W mode respectively.

#### **Application information (Continue)**

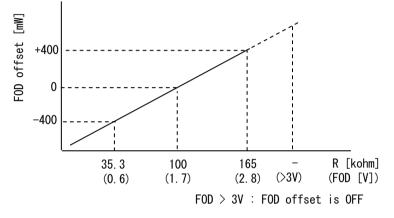

3. Foreign Object Detection offset setting : FOD (Pin No. E3)

The Foreign Object Detection function was added from WPC Ver.1.1.

In WPC ver 1.1, Foreign Object is judged by the Received Power (sent and calculated by secondary side) compared to the Transmitted Power by the primary side. In order to facilitate different structures/housing for the secondary side, AN32257A can add/subtract an offset for the received power through the FOD terminal.

As an example, when 100kohm is placed in between FOD terminal and GND, the offset value will be 0 (Refer to the chart below).

If this function is not required, please tied the FOD to VREG34V to disable it.

4. Frequency of a secondary coil : EXTCLK (Pin No. C4)

The frequency of the secondary coil is computed when EXTCLK terminal is provided with a clock frequency of 4MHz ~ 19MHz. The level of the input should be Vin. Subsequent, this computation will begin when register 0Ah is written 01h. The computation takes approximately 3ms.

User should read register 09h for the computed value. After which, frequency of the secondary coil can be calculated as follows:

Frequency of a secondary coil = Fextclk / FREQCNT[7:0]

(Refer to page 28 for more details)

### **Application information (Continue)**

5. Target control of VRECT voltage.

#### 5W mode

OUT=5V setup : SELHV = OPEN

Note) The above is a value of reference.

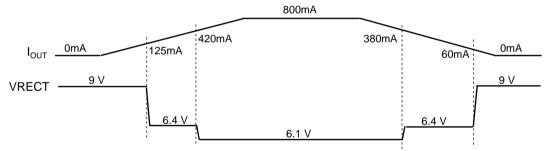

OUT=6V setup : SELHV = VREG34V

Note) The above is a value of reference.

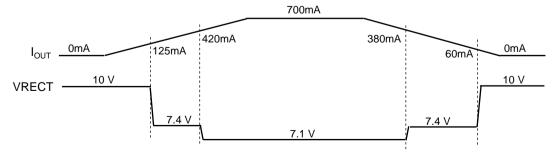

OUT=7V setup : SELHV = GND

Note) The above is a value of reference.

### **Application information (Continue)**

6. LED Indication

| Status                     | Indication |

|----------------------------|------------|

| Status                     | LED        |

| Standby                    | OFF        |

| Charge                     | ON         |

| Full Battery Detection     | OFF        |

| External Input Detection   | OFF        |

| Over-current Detection     | OFF        |

| Over-temperature Detection | OFF        |

#### **Product Standards**

# AN32257A

## Application information (Continue)

#### 7. Register MAP

#### Normal register

| Address        | R/W | RESET要因 | attribute            | bit7  | bit6  | bit5     | bit4       | bit3 | bit2 | bit1     | bit0      |

|----------------|-----|---------|----------------------|-------|-------|----------|------------|------|------|----------|-----------|

| 01h            | R   | NRESET  | SIGNALSTR            |       | 1     |          | SSV        |      | -    | -        |           |

| Initial<br>02h |     | _       |                      | 0     | 0     | 0        | 0<br>EPTP  | 0    | 0    | 0        | 0         |

| Initial        | R   | NRESET  | EPTP                 | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 03h            |     |         | CONTROL              | 0     | U     | 0        | CERF       | -    | 0    | 0        | 0         |

| Initial        | R   | NRESET  | CONTROL<br>ERROR     | 0     | 0     | 0        |            | 0    | 0    | 0        | 0         |

| 04h            |     |         |                      | 0     | 0     | 0        | RPWF       | -    | 0    | 0        | 0         |

| Initial        | R   | NRESET  | RECEIVED<br>POWER    | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 20h            |     |         |                      | 0     | 0     | 0        |            | -    | 0    | 0        | 0         |

| Initial        | R/W | NRESET  | CONTROL<br>POINT A   | 0     | 1     | 1        | 0          | 0    | 1    | 1        | 0         |

| 21h            |     |         |                      | 0     | 1     | I        |            | -    | I    | I        | 0         |

| Initial        | R/W | NRESET  | CONTROL<br>POINT B   | 0     | 1     | 0        | 0          |      | 1    | 0        | 1         |

| 22h            |     |         |                      | 0     | 1     | 0        | CTLPOIN    | -    | I    | 0        |           |

| Initial        | R/W | NRESET  | CONTROL<br>POINT C   | 0     | 1     | 0        | 0          |      | 0    | 0        | 1         |

| 23h            |     |         |                      | 0     | 1     | 0        | THRESH     | -    | 0    | 0        | 1         |

| Initial        | R/W | NRESET  | CURRENT<br>THRESH 1A | 0     | 0     | 0        | 1          | 0    | 0    | 0        | 0         |

| 24h            |     |         |                      | 0     | 0     | 0        | THRESH     | -    | 0    | 0        | 0         |

| Initial        | R/W | NRESET  | CURRENT<br>THRESH 1B | 0     | 0     | 0        | 0          | 1    | 0    | 0        | 0         |

| 25h            |     |         | CURRENT              | 0     | 0     | 0        | THRESH     | -    | 0    | 0        | 0         |

| Initial        | R/W | NRESET  | THRESH 2A            | 0     | 0     | 1        | 1          | 0    | 1    | 1        | 0         |

| 26h            |     |         | CURRENT              | 0     | 0     | I        | THRESH     | -    | 1    | 1        | 0         |

| Initial        | R/W | NRESET  | THRESH 2B            | 0     | 0     | 1        | 1          | 0    | 0    | 0        | 0         |

| 27h            |     |         |                      |       |       |          |            |      |      |          | TXEPTP    |

| Initial        | W   | NRESET  | TXEPTP               | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 40h            |     |         |                      |       |       |          | -          |      |      |          | PRIVILEGE |

| Initial        | R/W | NRESET  | USER MODE<br>SELECT  | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 71h            |     |         |                      | 0     | MAJOR | -        | 0          | 0    |      | VER[3:0] | 0         |

| Initial        | R   | NRESET  | ID1                  | 0     | 0     | 0        | 1          | 0    | 0    | 0        | 1         |

| 72h            |     |         |                      | 0     | 0     | 0        | MANUFACTUR | -    | 0    | 0        |           |

| Initial        | R   | NRESET  | ID2                  | 0     | 0     | 0        |            |      | 0    | 0        | 0         |

| 73h            |     |         |                      | č     |       | , ů      | MANUFACTU  | -    | , ů  | , ů      | , ů       |

| Initial        | R   | NRESET  | ID3                  | 0     | 0     | 1        | 0          | 0    | 1    | 0        | 1         |

| 74h            |     |         |                      | EXTID |       |          |            |      |      | , ů      | · · ·     |

| Initial        | R   | NRESET  | ID4                  | 0     | 0     | 0        | 0          |      | 0    | 0        | 0         |

| 75h            |     |         |                      | 0     | 0     | 0        | BASIC DEVI | -    | 0    | 0        |           |

| Initial        | R   | NRESET  | ID5                  | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 76h            |     |         |                      | č     |       | , ů      | BASIC DEVI | -    | Ŭ Ŭ  | , ů      | , ů       |

| Initial        | R   | NRESET  | ID6                  | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 77h            |     |         |                      |       |       | <u> </u> | BASIC DEV  | -    | Ŭ    | , ů      |           |

| Initial        | R   | NRESET  | ID7                  | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| 80h            |     |         | CHARGE               |       |       | _        |            |      |      |          | 10W MODE  |

| Initial        | R   | NRESET  | MODE                 | 0     | 0     | 0        | 0          | 0    | 0    | 0        | 0         |

| indur          |     |         |                      | v     | L V   | U U      | L V        | , v  | U U  |          | , v       |

#### **Product Standards**

## Application information (Continue)

7. Register MAP (Continue)

#### Privilege register

| Address | R/W    | RESET要因   | attribute        | bit7                                  | bit6       | bit5        | bit4         | bit3         | bit2              | bit1         | bit0              |

|---------|--------|-----------|------------------|---------------------------------------|------------|-------------|--------------|--------------|-------------------|--------------|-------------------|

| 03h     |        |           | CONTROL          | CERR7                                 | CERR6      | CERR5       | CERR4        | CERR3        | CERR2             | CERR1        | CERR0             |

| Initial | R/W    | PRIVILEGE | ERROR            | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 04h     |        |           | RECEIVED         | RPWR7                                 | RPWR6      | RPWR5       | RPWR4        | RPWR3        | RPWR2             | RPWR1        | RPWR0             |

| Initial | R/W    | PRIVILEGE | POWER            | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 05h     |        |           | CHARGE           | _                                     | -          | -           | CHGSTA       | TUS[7:0]     | -                 |              | -                 |

| Initial | R/W    | PRIVILEGE | STATUS           | 1                                     | 1          | 1           | 1            | 1            | 1                 | 1            | 1                 |

| 07h     |        |           | 0                | VADC7                                 | VADC6      | VADC5       | VADC4        | VADC3        | VADC2             | VADC1        | VADC0             |

| Initial | R      | PRIVILEGE | VADC             | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 08h     |        |           |                  | IADC7                                 | IADC6      | IADC5       | IADC4        | IADC3        | IADC2             | IADC1        | IADC0             |

| Initial | R      | PRIVILEGE | IADC             | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 09h     |        |           |                  |                                       | 0          | 0           | FREQC        |              | 0                 | 0            | 0                 |

| Initial | R      | PRIVILEGE | FREQCNT          | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

|         |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            |                   |

| 0Ah     | R/W    | PRIVILEGE | EXTCLK<br>ENABLE |                                       | _          | _           | _            |              |                   |              | EXTCLKEN          |

| Initial |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 30h     | R/W    | PRIVILEGE | CTLP 10W         |                                       |            |             | 10WCTLPC     |              |                   |              | -                 |

| Initial |        |           | VRECA            | 0                                     | 1          | 1           | 0            | 0            | 1                 | 1            | 0                 |

| 31h     | R/W    | PRIVILEGE | CTLP 10W         | <u> </u>                              | 1          |             | 10WCTLPC     |              |                   | 1            |                   |

| Initial |        |           | VRECB            | 0                                     | 1          | 1           | 0            | 0            | 1                 | 1            | 0                 |

| 32h     | R/W    | PRIVILEGE | CTLP 10W         |                                       |            |             | 10WCTLPC     | DINTC[7:0]   |                   |              |                   |

| Initial | 1011   | TIMEEOE   | VRECC            | 0                                     | 1          | 0           | 0            | 0            | 0                 | 0            | 1                 |

| 33h     | R/W    | PRIVILEGE | CTLP KEY         |                                       | _          |             |              |              |                   | _            | CTLPKEY           |

| Initial | 1.7.00 |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 41h     | DAA/   | PRIVILEGE | FUNCTION         | —                                     | _          | —           | —            | _            | _                 | SETRPWR      | SETCE             |

| Initial | R/W    | PRIVILEGE | SET              | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 42h     |        |           | POWER            |                                       |            |             | KA[7         | 7:0]         |                   |              |                   |

| Initial | R/W    | NRESET    | PARAMETER        | 0                                     | 0          | 0           | 0            | 1            | 1                 | 0            | 0                 |

| 43h     |        |           | 1<br>POWER       |                                       |            | -           | -            |              |                   | -            |                   |

|         | R/W    | NRESET    | PARAMETER        |                                       |            |             | KB[7         | -            |                   |              |                   |

| Initial |        |           | 2                | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 1                 |

| 44h     | BAA    | NDECET    | POWER            |                                       |            |             | KC[7         | 7:0]         |                   |              |                   |

| Initial | R/W    | NRESET    | PARAMETER<br>3   | 0                                     | 0          | 0           | 0            | 1            | 1                 | 1            | 1                 |

| 45h     |        |           | POWER            |                                       |            |             | OFFSE        | T[7:0]       |                   |              |                   |

| Initial | R/W    | NRESET    | OFFSET           | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 51h     |        |           |                  | -                                     | PWR CLASS0 | MAXPWR5     | MAXPWR4      | MAXPWR3      | MAXPWR2           | MAXPWR1      | MAXPWR0           |

| Initial | R      | PRIVILEGE | CONFIG1          | 0                                     | 0          | 0           | 0            | 1            | 0                 | 1            | 0                 |

| 53h     |        |           |                  |                                       |            |             |              |              | COUNT2            | COUNT1       | COUNTO            |

| Initial | R/W    | PRIVILEGE | CONFIG3          | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 54h     |        |           |                  |                                       |            | WINDOW SIZE | 0            |              |                   |              |                   |

| Initial | R/W    | PRIVILEGE | CONFIG4          | 1                                     | 0          | 0           | 0            | 0            | 1                 |              | 0                 |

| 60h     |        |           |                  |                                       |            |             | U            |              |                   | 0            | OPTREQ            |

| -       | w      | AUTORST   | OPTREQ           | 0                                     |            |             | 0            | 0            | 0                 | 0            |                   |

| Initial |        |           |                  |                                       | 0          | 0           | 0<br>OPTCNT4 | 0<br>OPTCNT3 | 0<br>OPTCNT2      | 0<br>OPTCNT1 | 0<br>OPTCNT0      |

| 61h     | R/W    | PRIVILEGE | OPTCNT           |                                       |            |             |              |              |                   |              |                   |

| Initial |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 1            | 1                 |

| 62h     | R/W    | PRIVILEGE | OPTADR           |                                       | <u> </u>   | <u>^</u>    | OPTAD        |              |                   |              |                   |

| Initial |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 1                 | 1            | 0                 |

| 63h     | R/W    | PRIVILEGE | OPTDATA1         |                                       |            |             | OPTDAT       |              | -                 |              |                   |

| Initial |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 64h     | R/W    | PRIVILEGE | OPTDATA2         | ļ                                     |            |             | OPTDAT       |              |                   | 1            |                   |

| Initial |        |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 65h     | R/W    | PRIVILEGE | OPTDATA3         |                                       |            |             | OPTDAT       |              |                   |              |                   |

| Initial |        |           | 5 5, (1) (5      | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 66h     | R/W    | PRIVILEGE | OPTDATA4         |                                       |            |             | OPTDAT       | A4[7:0]      |                   |              |                   |

| Initial | 1.7.00 |           |                  | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 67h     |        |           | ODTDATTY         | _                                     | —          | —           | _            | OPT4TXWAIT   | <b>OPT3TXWAIT</b> | OPT2TXWAIT   | <b>OPT1TXWAIT</b> |

| Initial | R      | PRIVILEGE | OPTDATTX         | 0                                     | 0          | 0           | 0            | 0            | 0                 | 0            | 0                 |

| 71h     | D      |           |                  | MAJOR VER3                            | MAJOR VER2 | MAJOR VER1  | MAJOR VER0   | MINOR VER    | MINOR VER         | MINOR VER    | MINOR VER         |

| Initial | R/W    | PRIVILEGE | ID1              | 0                                     | 0          | 0           | 1            | 0            | 0                 | 0            | 1                 |

|         |        |           |                  | · · · · · · · · · · · · · · · · · · · |            |             |              |              | -                 |              | 1                 |

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation

| Registe        | er Name |      |      |      | SIGN | ALSTR |      |      |      |

|----------------|---------|------|------|------|------|-------|------|------|------|

| Sub<br>Address | R/W     | D7   | D6   | D5   | D4   | D3    | D2   | D1   | D0   |

| 01h            | R       | SSV7 | SSV6 | SSV5 | SSV4 | SSV3  | SSV2 | SSV1 | SSV0 |

| Default        | 00h     | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    |

D7-D0 : Signal Strength Value (0-255)

Signal Strength Value = VRECT Voltage /  $20 \times 255$

| Registe        | r Name |       |       |       | RP    | TP    |       |       |       |

|----------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Sub<br>Address | R/W    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| 02h            | R      | EPTP7 | EPTP6 | EPTP5 | EPTP4 | EPTP3 | EPTP2 | EPTP1 | EPTP0 |

| Default        | 00h    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

D7-D0: End Power Transfer Packet

The message contained in a "End Power Transfer packet" is shown.

0x00 : EXT input detection

0x01 : Full charge

0x02 : Internal Fault \*\* This can be set by writing 01h to register 27h.

0x03: Over temperature detection

0x04 : Over voltage detection

0x05 : Over current detection

| Registe        | r Name |       | CONTROLERROR |       |       |       |       |       |       |  |  |  |  |

|----------------|--------|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Sub<br>Address | R/W    | D7    | D6           | D5    | D4    | D3    | D2    | D1    | D0    |  |  |  |  |

| 03h            | R      | CERR7 | CERR6        | CERR5 | CERR4 | CERR3 | CERR2 | CERR1 | CERR0 |  |  |  |  |

| Default        | 00h    | 0     | 0            | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

D7-D0 : Control Error Value (-128 - +127)

### **Application information (Continue)**

#### 7. Register MAP (Continue)

Explanation (Continue)

| Registe        | r Name |       |       |       | RECEIVE | DPOWER |       |       |       |

|----------------|--------|-------|-------|-------|---------|--------|-------|-------|-------|

| Sub<br>Address | R/W    | D7    | D6    | D5    | D4      | D3     | D2    | D1    | D0    |

| 04h            | R      | RPWR7 | RPWR6 | RPWR5 | RPWR4   | RPWR3  | RPWR2 | RPWR1 | RPWR0 |

| Default        | 00h    | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

D7-D0 : Received Power Value(0-255)

The time range defined as the Configuration packet shows the average of the Power total amount which the secondary side received.

It is an integer of 0 to 255 without a mark.

Receiving Power's total amount is calculated below.

Received Power = (RPWR[7:0] / 128) × (Maximum Power / 2) ×  $10^{Power Class}$  W

\* The Configuration packet defines Maximum Power and Power Class.

| Registe        | r Name |                | CONTROLPOINT A |                |                |                |                |                |                |  |  |  |

|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| Sub<br>Address | R/W    | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |  |  |  |

| 20h            | R/W    | CTLPOINT<br>A7 | CTLPOINT<br>A6 | CTLPOINT<br>A5 | CTLPOINT<br>A4 | CTLPOINT<br>A3 | CTLPOINT<br>A2 | CTLPOINT<br>A1 | CTLPOINT<br>A0 |  |  |  |

| Default        | 66h    | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              |  |  |  |

D7-D0 : Control Point A(0-255)

The target value of VRECT voltage when current is less than 125mA is shown.

VRECT voltage is calculated below.

VRECT voltage = CTLPOINTA[7:0] / 255 × 20 V

\*Initial value : 8.0 V

| Registe        | r Name |                | CONTROLPOINT B |                |                |                |                |                |                |  |  |  |

|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| Sub<br>Address | R/W    | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |  |  |  |

| 21h            | R/W    | CTLPOINT<br>B7 | CTLPOINT<br>B6 | CTLPOINT<br>B5 | CTLPOINT<br>B4 | CTLPOINT<br>B3 | CTLPOINT<br>B2 | CTLPOINT<br>B1 | CTLPOINT<br>B0 |  |  |  |

| Default        | 45h    | 0              | 1              | 0              | 0              | 0              | 1              | 0              | 1              |  |  |  |

D7-D0: Control Point B(0-255)

The target value of VRECT voltage in case current is settled in the range of 125mA to 420mA is shown.

VRECT voltage is calculated below.

VRECT voltage = CTLPOINTB[7:0] / 255 × 20 V

\* Initial value : 5.4 V

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation (Continue)

| Registe        | r Name |                | CONTROLPOINT C |                |                |                |                |                |                |  |  |  |

|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| Sub<br>Address | R/W    | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |  |  |  |

| 22h            | R/W    | CTLPOINT<br>C7 | CTLPOINT<br>C6 | CTLPOINT<br>C5 | CTLPOINT<br>C4 | CTLPOINT<br>C3 | CTLPOINT<br>C2 | CTLPOINT<br>C1 | CTLPOINT<br>C0 |  |  |  |

| Default        | 41h    | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              |  |  |  |

D7-D0 : Control Point C(0-255)

The target value of VRECT voltage in case current is more than 420mA is shown.

VRECT voltage is calculated below.

VRECT voltage = CTLPOINTC[7:0] /  $255 \times 20$  V

\*Initial value : 5.1 V

| Registe        | r Name |               |               | CURRENTTHRESH 1A |               |               |               |               |               |  |  |  |  |  |

|----------------|--------|---------------|---------------|------------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|--|

| Sub<br>Address | R/W    | D7            | D6            | D5               | D4            | D3            | D2            | D1            | D0            |  |  |  |  |  |

| 23h            | R/W    | THRESH1A<br>7 | THRESH1A<br>6 | THRESH1A<br>5    | THRESH1A<br>4 | THRESH1A<br>3 | THRESH1A<br>2 | THRESH1A<br>1 | THRESH1A<br>0 |  |  |  |  |  |

| Default        | 10h    | 0             | 0             | 0                | 1             | 0             | 0             | 0             | 0             |  |  |  |  |  |

D7-D0 : Current thresh 1A(0-255)

It is a setting register of a Control Point A/B change current threshold value (higher).

A current threshold value is calculated below.

Current threshold = THRESH1A[7:0] /  $255 \times 2$  A

\* Initial value : 125mA

| Registe        | r Name |               |               |               | CURRENT       | THRESH 1B     |               |               |               |

|----------------|--------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Sub<br>Address | R/W    | D7            | D6            | D5            | D4            | D3            | D2            | D1            | D0            |

| 24h            | R/W    | THRESH1A<br>7 | THRESH1A<br>6 | THRESH1A<br>5 | THRESH1A<br>4 | THRESH1A<br>3 | THRESH1A<br>2 | THRESH1A<br>1 | THRESH1A<br>0 |

| Default        | 08h    | 0             | 0             | 0             | 0             | 1             | 0             | 0             | 0             |

D7-D0 : Current thresh 1B(0-255)

It is a setting register of a Control Point A/B change current threshold value (lower).

A current threshold value is calculated below.

Current threshold = THRESH1B[7:0] /  $255 \times 2$  A

\* Initial value : 60mA

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation (Continue)

| Registe        | r Name |               |               |               | CURRENT       | THRESH 2A     |               |               |               |

|----------------|--------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Sub<br>Address | R/W    | D7            | D6            | D5            | D4            | D3            | D2            | D1            | D0            |

| 25h            | R/W    | THRESH2A<br>7 | THRESH2A<br>6 | THRESH2A<br>5 | THRESH2A<br>4 | THRESH2A<br>3 | THRESH2A<br>2 | THRESH2A<br>1 | THRESH2A<br>0 |

| Default        | 36h    | 0             | 0             | 1             | 1             | 0             | 1             | 1             | 0             |

D7-D0 : Current thresh 2A(0-255)

It is a setting register of a Control Point B/C change current threshold value (higher).

A current threshold value is calculated below.

Current threshold = THRESH2A[7:0] /  $255 \times 2$  A

\* Initial value : 420mA

| Registe        | r Name |               |               |               | CURRENT       | THRESH 2B     |               |               |               |

|----------------|--------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Sub<br>Address | R/W    | D7            | D6            | D5            | D4            | D3            | D2            | D1            | D0            |

| 26h            | R/W    | THRESH2A<br>7 | THRESH2A<br>6 | THRESH2A<br>5 | THRESH2A<br>4 | THRESH2A<br>3 | THRESH2A<br>2 | THRESH2A<br>1 | THRESH2A<br>0 |

| Default        | 30h    | 0             | 0             | 1             | 1             | 0             | 0             | 0             | 0             |

D7-D0: Current thresh 2B(0-255)

It is a setting register of a Control Point B/C change current threshold value (lower).

A current threshold value is calculated below.

Current threshold = THRESH2B[7:0] /  $255 \times 2$  A

\* Initial value : 380mA

| Registe        | er Name |    | ТХЕРТР |    |    |    |    |    |        |  |  |  |

|----------------|---------|----|--------|----|----|----|----|----|--------|--|--|--|

| Sub<br>Address | R/W     | D7 | D6     | D5 | D4 | D3 | D2 | D1 | D0     |  |  |  |

| 27h            | W       | -  | -      | -  | -  | -  | -  | -  | TXEPTP |  |  |  |

| Default        | 00h     | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 0      |  |  |  |

D0 : TXEPTP

It is a compulsive transmitting register of an End Power Transfer packet.

0 : Normal operation (default)

$1\,:\, End$  Power Transfer packet transmission

\* This register will automatically clear after sending the End Power Transfer packet.

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation (Continue)

| Registe        | er Name |    | USER MORE SELECT |    |    |    |    |    |           |  |  |  |  |

|----------------|---------|----|------------------|----|----|----|----|----|-----------|--|--|--|--|

| Sub<br>Address | R/W     | D7 | D6               | D5 | D4 | D3 | D2 | D1 | D0        |  |  |  |  |

| 40h            | R/W     | -  | -                | -  | -  | -  | -  | -  | PRIVILEGE |  |  |  |  |

| Default        | 00h     | 0  | 0                | 0  | 0  | 0  | 0  | 0  | 0         |  |  |  |  |

#### D0 : PRIVILEGE

This register controls the access to privilege register.

0 : Normal register map access only. (default)

1 : Access to privilege register and normal register.

| Registe        | r Name |    | ID1   |          |    |                |    |    |    |  |

|----------------|--------|----|-------|----------|----|----------------|----|----|----|--|

| Sub<br>Address | R/W    | D7 | D6    | D5       | D4 | D3             | D2 | D1 | D0 |  |

| 71h            | R      |    | MAJOR | VER[3:0] |    | MINOR VER[3:0] |    |    |    |  |

| Default        | 00h    | 0  | 0     | 0        | 1  | 0              | 0  | 0  | 1  |  |

D7-D4 : MAJOR VER[3:0]

Major Version of the WPC standard to which this LSI corresponds is shown. 0001 : Major Version (default)

D3-D0 : MINOR VER[3:0]

Minor Version of the WPC standard to which this LSI corresponds is shown. 0001 : Minor Version (default)

| Registe        | r Name |                 | ID2               |    |           |              |    |    |    |  |  |  |

|----------------|--------|-----------------|-------------------|----|-----------|--------------|----|----|----|--|--|--|

| Sub<br>Address | R/W    | D7              | D6                | D5 | D4        | D3           | D2 | D1 | D0 |  |  |  |

| 72h            | R      |                 |                   | Ν  | IANUFACTU | RE CODE[15:8 | 8] |    |    |  |  |  |

| Default        | 00h    | 0               | 0 0 0 0 0 0 0 0 0 |    |           |              |    |    |    |  |  |  |

| Registe        | r Name |                 |                   |    | IC        | 03           |    |    |    |  |  |  |

| Sub<br>Address | R/W    | D7              | D6                | D5 | D4        | D3           | D2 | D1 | D0 |  |  |  |

| 73h            | R      |                 |                   | 1  | MANUFACTU | RE CODE[7:0  | )] |    |    |  |  |  |

| Default        | 25h    | 0 0 1 0 0 1 0 1 |                   |    |           |              |    |    |    |  |  |  |

REGISTER 72h-73h[7:0] : MANUFACTURE CODE

Manufacture Code of Panasonic is shown.

0025 : Manufacture Code of Panasonic (default)

### **Application information (Continue)**

#### 7. Register MAP (Continue)

#### Explanation (Continue)

| Registe        | er Name |       |                                                                      |    | ID         | 9 4          |        |    |    |

|----------------|---------|-------|----------------------------------------------------------------------|----|------------|--------------|--------|----|----|

| Sub<br>Address | R/W     | D7    | D6                                                                   | D5 | D4         | D3           | D2     | D1 | D0 |

| 74h            | R       | EXTID |                                                                      |    | BASIO      | C DEVICE ID[ | 30:24] |    |    |

| Default        | 00h     | 0     | 0                                                                    | 0  | 0          | 0            | 0      | 0  | 0  |

| Registe        | r Name  |       |                                                                      |    | ID         | 5            |        |    |    |

| Sub<br>Address | R/W     | D7    | D6                                                                   | D5 | D4         | D3           | D2     | D1 | D0 |

| 75h            | R       |       |                                                                      |    | BASIC DEVI | CE ID[23:16] |        |    |    |

| Default        | 0Xh     | 0     | 0                                                                    | 0  | 0          | X            | X      | Х  | Х  |

| Registe        | er Name |       |                                                                      |    | IC         | 06           |        |    |    |

| Sub<br>Address | R/W     | D7    | D6                                                                   | D5 | D4         | D3           | D2     | D1 | D0 |

| 76h            | R       |       |                                                                      |    | BASIC DEV  | ICE ID[15:8] |        |    |    |

| Default        | XXh     | X     | X                                                                    | X  | X          | X            | X      | X  | Х  |

| Registe        | er Name |       |                                                                      |    | IC         | )7           |        |    |    |

| Sub<br>Address | R/W     | D7    | D6         D5         D4         D3         D2         D1         D0 |    |            |              |        |    |    |

| 77h            | R       |       |                                                                      |    | BASIC DEV  | /ICE ID[7:0] |        |    |    |

| Default        | XXh     | X     | X X X X X X X X                                                      |    |            |              |        |    |    |

REGISTER 74h[7] : Extended ID

The identification bit sequence of this LSI is chosen.

0 : Manufacturer Code || Basic Device ID

1 : Manufacturer Code || Basic Device ID || Extended Device Identifier

REGISTER 74h-77h Basic Device ID[30:0]

Basic Device ID of this LSI is shown.

A random number is set to BASIC DEVICE ID [19:0].

| Registe        | er Name |    | CHRGE MODE |    |    |    |    |    |         |  |  |  |  |

|----------------|---------|----|------------|----|----|----|----|----|---------|--|--|--|--|

| Sub<br>Address | R/W     | D7 | D6         | D5 | D4 | D3 | D2 | D1 | D0      |  |  |  |  |

| 80h            | R       | -  | -          | -  | -  | -  | -  | -  | 10WMODE |  |  |  |  |

| Default        | 00h     | 0  | 0          | 0  | 0  | 0  | 0  | 0  | 0       |  |  |  |  |

(default)

D0:10W MODE

It is a register which shows the 10W mode.

By setup of SELHP=H, when the primary side corresponds (NN32251A), it becomes "H".

0:5W mode (default)

1:10W mode

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation (Continue)

#### Privilege register

| Registe        | er Name |       | CONTROLERROR |       |       |       |       |       |       |  |  |  |

|----------------|---------|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

| Sub<br>Address | R/W     | D7    | D6           | D5    | D4    | D3    | D2    | D1    | D0    |  |  |  |

| 03h            | R/W     | CERR7 | CERR6        | CERR5 | CERR4 | CERR3 | CERR2 | CERR1 | CERR0 |  |  |  |

| Default        | 00h     | 0     | 0            | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

D7-D0 : Control Error Value (-128 - +127)

The contents of the Control Error packet are shown.

It is a signed integer of -128 to +127 in the complement form of 2.

By set up SETCE (Address41h, bit0) ="H", the Control Error value written in this address is transmit.

| Registe        | r Name |       | RECEIVEDPOWER |       |       |       |       |       |       |  |  |  |

|----------------|--------|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|

| Sub<br>Address | R/W    | D7    | D6            | D5    | D4    | D3    | D2    | D1    | D0    |  |  |  |

| 04h            | R/W    | RPWR7 | RPWR6         | RPWR5 | RPWR4 | RPWR3 | RPWR2 | RPWR1 | RPWR0 |  |  |  |

| Default        | 00h    | 0     | 0             | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

D7-D0 : Received Power Value(0-255)

The time range defined as the Configuration packet shows the average of the power total amount which the secondary side received. It is an integer of 0 to 255 without a mark.

The total amount of receiving power is calculated below.

Received Power = (RPWR[7:0] / 128) × (Maximum Power / 2) ×  $10^{Power Class}$  W

By set up SETRPWR (Address41h, bit1) ="H", the Received Power value written in this address is transmit.

\* The Configuration packet defines Maximum Power and Power Class.

### **Application information (Continue)**

7. Register MAP (Continue)

Explanation (Continue)

#### **Privilege register**

| Registe        | r Name |                | CHARGE STATUS  |                |                |                |                |                |                |  |  |  |  |

|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|--|

| Sub<br>Address | R/W    | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |  |  |  |  |

| 05h            | R/W    | CHGSTAT<br>US7 | CHGSTAT<br>US6 | CHGSTAT<br>US5 | CHGSTAT<br>US4 | CHGSTAT<br>US3 | CHGSTAT<br>US2 | CHGSTAT<br>US1 | CHGSTAT<br>US0 |  |  |  |  |

| Default        | FFh    | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              |  |  |  |  |

D7-D0 : Charge Status Value(0-100, 255)

The rate to a full charge level is shown.

00000000 : Empty

:

01100100 : Full charge

11111111 : Charge information cannot be given. (default)

| Registe        | r Name |       | CONTROLERROR |       |       |       |       |       |       |  |  |  |

|----------------|--------|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

| Sub<br>Address | R/W    | D7    | D6           | D5    | D4    | D3    | D2    | D1    | D0    |  |  |  |

| 07h            | R      | VADC7 | VADC6        | VADC5 | VADC4 | VADC3 | VADC2 | VADC1 | VADC0 |  |  |  |